目次

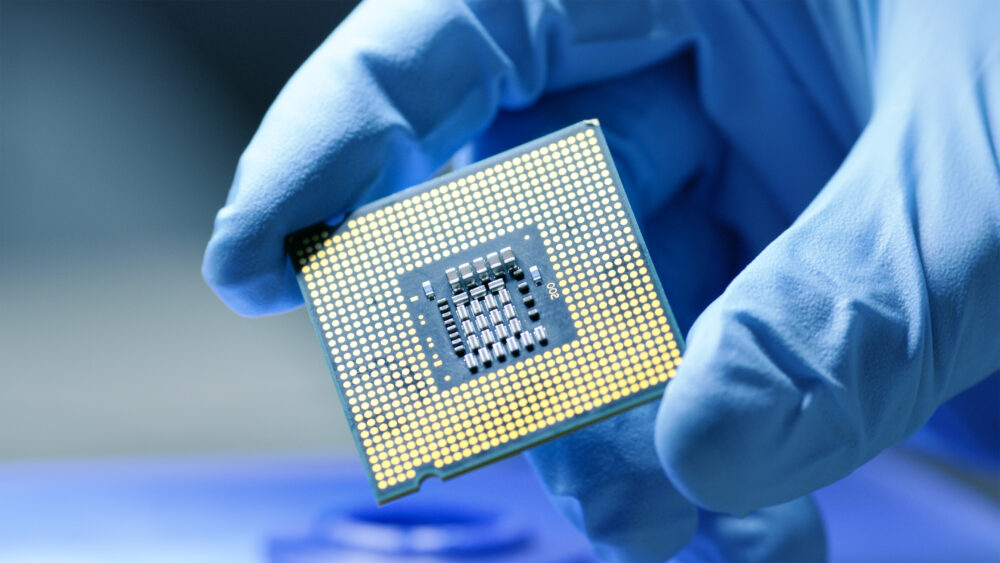

半導体製造工程の概要

半導体の製造工程を理解するためには、まずその全体像を把握することが不可欠です。ここでは、半導体製造工程の概要について説明します。

半導体製造の全体像

半導体の製造工程は、大きく分けて3つの段階から成り立っています。まず、シリコン単結晶の基板を作る「シリコンウエハーの製造工程」、次にシリコンウエハー上に半導体チップを作り込む「前工程」、最後にチップを切り出してパッケージ化し完成させる「後工程」です。

- 関連記事:パーティクル問題解決の最前線!半導体品質向上のための対策術

- 関連記事:【FOUPがもたらす半導体革新】品質管理はどう変わる?

- 関連記事:【バッチ式vs枚葉式】半導体製造装置の2大方式を徹底比較

- 関連記事:半導体製造装置が丸わかり!装置選びのポイントと選定のコツ

- 関連記事:MES導入で生産性向上!活用法を3つご紹介

- 関連記事:MES(製造実行システム)とは?導入のメリットや事例、ERPとの違い

- 関連記事:MES活用例:「設備・人の稼働データ」と「工程実績データ」

これらの工程は、高度に洗練された技術の集大成であり、各工程が緊密に連携することで、現代の電子機器に不可欠な高性能・高品質の半導体チップが生み出されるのです。特に、前工程のクリーンルーム環境での微細加工技術は、半導体の性能と信頼性を左右する極めて重要な要素となっています。

シリコンウエハーの製造プロセス

シリコンウエハーの製造は、高純度シリコンの原料となる珪石の採取から始まります。採取された珪石は、電気炉での還元分解により金属シリコンへと変換されます。この金属シリコンは、化学処理(シーメンス法)によって超高純度化され、多結晶シリコンとなります。

次に、このシリコンをチョクラルスキー法(CZ法)で溶融・凝固させ、単結晶シリコンインゴットを製造します。最後に、インゴットをスライス、研削、研磨することで、半導体製造の出発点となるシリコンウエハーが完成します。この一連のプロセスにより、高品質で均一な特性を持つシリコンウエハーが供給されます。

前工程と後工程の役割

前工程では、シリコンウエハー上に複雑な回路パターンを形成し、半導体チップを作り上げていきます。この工程では、洗浄、成膜、フォトリソグラフィ、エッチング、イオン注入、熱処理、平坦化など、多岐にわたる高度な技術が駆使されます。これらの工程を経て、ウエハー上には数多くのチップが形成されていきます。

一方、後工程は、前工程で完成したウエハーをチップ単位に切り出し、パッケージ化して製品として仕上げる役割を担います。ダイシング、ダイボンディング、ワイヤーボンディング、モールド、検査などの工程を経て、半導体チップが最終製品として完成します。

このように、前工程と後工程は、それぞれが重要な役割を果たしながら、半導体製造という一つの大きなプロセスを形作っているのです。両工程の緊密な連携と、高度な技術の結集により、私たちの生活を支える多様な半導体製品が生み出されています。

シリコンウエハーの製造工程の詳細

半導体製造の起点となるシリコンウエハーは、原料の採取から単結晶化、そしてウエハーへの加工まで、一連の高度な製造工程を経て生み出されます。ここでは、シリコンウエハーができるまでの詳細な製造プロセスについて解説します。

原料採取と金属シリコン生成

シリコンウエハーの原料となるのは、珪石と呼ばれる二酸化ケイ素(SiO2)を主成分とする鉱石です。高純度の珪石を採掘し、これを電気炉内で還元剤とともに高温で処理することで、98〜99%の純度を持つ金属シリコンが生成されます。

この金属シリコンは、半導体グレードの純度には至っていないため、さらなる精製が必要となります。精製方法としては、次に説明する化学的な処理が一般的です。

多結晶シリコンの製造方法

金属シリコンを半導体グレードの超高純度シリコンへと精製するプロセスが、多結晶シリコンの製造です。代表的な手法として、シーメンス法が広く用いられています。

シーメンス法では、金属シリコンを塩化水素ガスと反応させ、三塩化シランを合成します。この三塩化シランを1,000℃以上の高温に保たれた電気炉内のシリコン芯棒上で熱分解することで、純度99.9999999%(9N)以上の多結晶シリコンが芯棒表面に析出します。

こうして得られた多結晶シリコンは、半導体チップ製造に適した高純度ですが、結晶構造が不規則であるため、そのままではウエハーとして使用できません。単結晶化が次の重要な工程となります。

単結晶シリコンインゴットの製造方法

多結晶シリコンから半導体ウエハーの基材となる単結晶シリコンを作製するには、チョクラルスキー法(CZ法)が用いられます。CZ法は、るつぼ内で溶融した多結晶シリコンに種結晶を接触させ、ゆっくりと引き上げることで、単結晶シリコンの柱状固体(インゴット)を成長させる方法です。

CZ法の工程では、るつぼ内のシリコン溶湯の温度や、引き上げ速度、種結晶の回転速度などを高度に制御することで、直径30cm以上、長さ2m以上の大型の単結晶インゴットを得ることができます。この大型化により、ウエハーの大口径化と歩留まりの向上が可能となっています。

シリコンウエハー加工の流れ

CZ法で製造された単結晶シリコンインゴットは、以下の工程を経てウエハーへと加工されます。

- スライシング:ダイヤモンド刃やワイヤーソーを用いて、インゴットを薄く輪切りにし、ウエハー状に成形。

- ラッピング:スライスされたウエハー表面の凹凸を砥石で粗削りし、平坦化。

- エッチング:ラッピングで生じたダメージ層を薬液で除去。

- ポリッシング:ウエハー表面を鏡面状に研磨。

- 洗浄:パーティクルや金属不純物を除去し、清浄なウエハーを完成。

以上の工程を経て、半導体チップの製造に適した高品質のシリコンウエハーが完成します。シリコンウエハーの品質は、その後の半導体デバイスの性能や歩留まりに直結するため、各工程での厳密な管理が不可欠なのです。

前工程(ウエハープロセス)の主要技術

前工程は、シリコンウエハー上に半導体チップを作り込む工程であり、半導体製造の中核を担っています。ここでは、前工程を構成する主要な技術要素について、それぞれの目的と方法を解説していきます。

洗浄工程の目的と方法

洗浄工程は、ウエハー表面に付着したパーティクルや有機物、金属不純物などの汚れを除去することを目的としています。これらの汚れは、回路の欠陥や特性劣化の原因となるため、高い清浄度を維持することが不可欠です。

洗浄方法としては、濃硫酸と過酸化水素水の混合液を用いるSPM洗浄や、アンモニア水と過酸化水素水の混合液を用いるSC1洗浄、希塩酸と過酸化水素水の混合液を用いるSC2洗浄などがあります。これらの薬液を使い分けることで、効果的な汚れの除去が可能となります。

また、超純水を用いた超音波洗浄や、ブラシ洗浄、スピン洗浄なども組み合わせて使用されます。洗浄後は、ウエハー表面の水分を完全に除去するために、高温の窒素(N2)ガスを吹き付けるドライング処理が行われます。

成膜工程の種類と役割

成膜工程では、ウエハー上に各種の薄膜を形成します。これらの膜は、絶縁層、導電層、保護層などの役割を担っています。主な成膜技術としては、以下のようなものがあります。

- 熱酸化法:シリコンウエハーを高温の酸素雰囲気中で加熱し、表面に二酸化シリコン膜を形成。

- CVD法:原料ガスを反応させ、ウエハー上に膜を堆積。酸化膜、窒化膜、ポリシリコン膜などの形成に使用。

- PVD法:ターゲット材料をスパッタリングやイオンプレーティングにより蒸発させ、ウエハー上に薄膜を堆積。

これらの成膜技術を駆使し、トランジスタのゲート絶縁膜や配線層間の絶縁膜、ソース・ドレイン電極、ゲート電極などを形成していきます。膜質や膜厚の制御は、デバイスの特性や信頼性に直結するため、高度な管理が必要とされます。

フォトリソグラフィ工程の原理

フォトリソグラフィ工程は、回路パターンをウエハー上に転写する技術です。まず、ウエハー上に感光性樹脂であるフォトレジストを塗布します。次に、回路パターンが描かれたフォトマスクを通して紫外線を照射すると、照射部のフォトレジストが溶解性を変化させます。

現像液で処理することで、溶解性の変化した部分のフォトレジストが選択的に除去され、フォトマスク上のパターンがフォトレジスト上に転写されます。このフォトレジストパターンをマスクとして、その下の膜をエッチングすることで、回路パターンを形成していきます。

フォトリソグラフィ工程では、縮小投影露光装置であるステッパーやスキャナーが使用されます。露光波長の短波長化や、液浸露光、多重露光などの技術により、微細パターンの形成が可能となっています。

エッチング工程の種類と特徴

エッチング工程は、フォトリソグラフィで形成したレジストパターンをマスクとして、その下の不要な部分の膜や基板を選択的に取り除く技術です。エッチング方式としては、以下のようなものがあります。

- ウェットエッチング:薬液を用いて化学的に材料を溶解させる方法。等方的にエッチングが進行。

- ドライエッチング:プラズマを用いて物理的・化学的に材料を除去する方法。異方性が高く、微細加工に適している。

- 反応性イオンエッチング(RIE):反応性ガスのプラズマを用いる方法。

- 誘導結合プラズマ(ICP)エッチング:高密度プラズマを用いる方法。

ドライエッチングでは、エッチング速度や選択比、物理的特性が方向によって異なる異方性などを制御することが重要です。また、エッチング後のレジスト除去や、エッチング残渣の除去にも注意が必要です。高アスペクト比の微細パターンを形成するためには、プロセス条件の最適化が不可欠となります。

イオン注入工程による特性制御

イオン注入工程は、シリコン基板中に不純物元素を導入し、電気的特性を制御する技術です。不純物元素としては、リンやヒ素などのn型不純物、ボロンなどのp型不純物が用いられます。イオン注入には、以下のような特徴があります。

- 不純物濃度や分布を精密に制御できる。

- 自己整合的にソース・ドレイン領域を形成できる。

- 注入後の熱処理により、結晶欠陥の回復や不純物の活性化が必要。

イオン注入の条件(エネルギー、ドーズ量、傾斜角など)を最適化することで、トランジスタの閾値電圧や寄生抵抗、耐圧などの特性を制御します。また、ポケット注入や拡張ソース・ドレイン構造の形成にも利用されます。

熱処理工程の効果と方法

熱処理工程は、ウエハーに熱エネルギーを与えることで、結晶欠陥の回復や不純物の活性化、膜質の改善などを図る技術です。主な熱処理方法としては、以下のようなものがあります。

- ランプアニール:ハロゲンランプやキセノンランプを用いて急速加熱・冷却する方法。イオン注入後の活性化に使用。

- レーザーアニール:レーザー光を照射してウエハー表面を局所的に加熱する方法。浅い接合形成や結晶化に使用。

- 熱酸化:高温の酸素雰囲気中で加熱し、シリコン表面を酸化させる方法。ゲート絶縁膜の形成などに使用。

熱処理の温度や時間、雰囲気などを最適化することで、結晶欠陥密度の低減や不純物の活性化率の向上、界面準位密度の低減などを図ります。また、急速熱処理を用いることで、熱予算を抑えつつ、高品質な膜質や接合を得ることが可能となります。

CMOS製造プロセスフロー

CMOS(Complementary Metal-Oxide-Semiconductor)は、現代の集積回路(IC)で最も広く使用されているトランジスタ技術です。ここでは、CMOSデバイスがシリコンウエハー上でどのように製造されるかについて、その工程の流れを詳しく解説します。

CMOS製造プロセスは、大きく分けてウエハー準備、酸化膜形成、パターニング、イオン注入、配線・絶縁膜形成、保護膜形成の6つのステップで構成されています。各工程では、フォトリソグラフィ、エッチング、成膜、熱処理などの様々な技術が駆使され、ナノメートルスケールの精密な加工が行われます。

CMOSトランジスタの基本構造

CMOSトランジスタは、NMOS(N型MOS)とPMOS(P型MOS)の2種類のトランジスタを組み合わせた相補的な構造を持っています。これにより、低消費電力、高速動作、高集積化が可能となります。

基本的な構造は、シリコン基板上にソース、ドレイン、ゲート電極、ゲート酸化膜が形成されています。NMOSとPMOSでは、ソースとドレインに注入する不純物の種類(NMOSはリン、PMOSはボロン)が異なります。

ウエハー準備から酸化膜形成まで

まず、高純度の単結晶シリコンウエハーを準備し、表面の汚れや自然酸化膜を除去するためにRCA洗浄を行います。次に、シリコン表面に熱酸化法により高品質の酸化シリコン膜(SiO2)を形成します。この酸化膜は、トランジスタのゲート絶縁膜や素子間の分離に使用されます。

酸化膜の形成には、ドライ酸化(酸素雰囲気中)とウェット酸化(水蒸気雰囲気中)の2種類の方法があり、目的に応じて使い分けられます。ドライ酸化は高品質な膜が得られ、ウェット酸化は成長速度が速いという特徴があります。

フォトリソグラフィとエッチングによるパターニング

CMOSの回路パターンを形成するために、フォトリソグラフィ技術を使用します。まず、ウエハー表面に感光性樹脂(フォトレジスト)を塗布し、回路パターンが描かれたフォトマスクを通して紫外線を照射します。

露光されたフォトレジストは現像処理により溶解除去され、パターンが転写されます。次に、このレジストパターンをマスクとして、エッチング処理により不要な部分の酸化膜や金属膜を選択的に取り除き、回路パターンを形成します。

エッチングには、ウェットエッチング(薬液使用)とドライエッチング(プラズマ使用)の2種類があり、加工精度や材料に応じて使い分けられます。特に、プラズマを用いたドライエッチングは、高精度・高アスペクト比の加工に適しています。

イオン注入による特性付与

トランジスタの電気的特性を制御するために、イオン注入技術を用います。イオン注入は、加速器で生成した不純物イオンをシリコン基板に打ち込む技術です。NMOSにはリン、PMOSにはボロンを注入し、ソースとドレインを形成します。

イオン注入の条件(加速エネルギー、ドーズ量)を調整することで、不純物濃度と注入深さを精密に制御できます。また、注入後の熱処理(アニール)により、結晶欠陥の回復と不純物の活性化を行います。

配線と絶縁膜の形成プロセス

トランジスタ間の配線を形成するために、CVD(化学気相成長)法によりシリコン酸化膜や窒化膜などの絶縁膜を堆積します。絶縁膜上に、アルミニウムや銅などの金属膜をスパッタリング法で成膜し、フォトリソとエッチングにより配線パターンを形成します。

配線と絶縁膜の形成は、多層配線構造を実現するために繰り返し行われます。各層間の絶縁膜には、VIA(配線層間の接続孔)が形成され、上下の配線層を接続します。また、CMP(化学機械研磨)技術により、各層の表面を平坦化し、次の層の形成を容易にします。

保護膜形成と最終検査

最後に、チップ表面を保護するために、窒化シリコン(SiN)などの保護膜(パッシベーション膜)を形成します。保護膜には、ボンディングパッドの開口部が設けられ、ワイヤーボンディングを可能にします。

ウエハー上の全工程が完了したら、各チップの電気的特性を自動検査装置でテストします。不良チップにはインクでマークが付けられ、良品のみが後工程(ダイシング、パッケージング)に送られます。

以上が、CMOSデバイスの製造工程の概要です。半導体技術の進歩により、微細化が進み、より高性能・高機能なICチップが実現されています。

後工程(パッケージング)の詳細

前工程で完成したウエハーは、後工程(パッケージング)に送られ、最終製品として仕上げられます。後工程では、ダイシング、ダイボンディング、ワイヤーボンディング、モールド、検査の各工程を経て、ICパッケージが完成します。ここでは、これらの工程について詳しく解説していきます。

ダイシング工程でのチップ切り出し

ダイシング工程では、ウエハーをICチップ単位に切断します。この工程は、ダイサーと呼ばれる専用の装置を使って行われます。ダイサーは、高速回転するダイヤモンドブレードでウエハーを切断していきます。

ウエハーの表面には、切断ラインに沿ってストリートと呼ばれる溝が形成されています。ダイサーのブレードは、このストリートに沿って正確に切断していきます。切断された個々のICチップは、ダイスと呼ばれます。

ダイシング工程では、切断精度と切断面の品質が重要なポイントとなります。ブレードの位置合わせや切断条件の最適化により、高品質なダイスを得ることができます。また、切断時に発生するチッピングや割れを防ぐために、特殊な保護テープが使用されることもあります。

ダイボンディングとワイヤーボンディング

ダイボンディングは、切り出されたダイスをリードフレームやパッケージ基板に接着する工程です。ダイスの裏面には、導電性の接着剤が塗布され、リードフレームや基板に固定されます。この接着剤は、放熱性にも優れているため、ICチップの熱を効率的に逃がす役割も果たします。

ワイヤーボンディングは、ダイスとリードフレームの電極を金や銅などの細い金属ワイヤで接続する工程です。ボンディング装置のキャピラリと呼ばれる細い針で、ワイヤをダイスのボンディングパッドに熱圧着し、もう一方の端をリードフレームに接続します。この工程により、ICチップの内部回路と外部端子が電気的に接続されます。

ワイヤーボンディングでは、ワイヤの材質や太さ、ボンディング条件などが重要な要素となります。また、ボンディング装置の位置精度や速度も生産性に大きく影響します。近年では、金ワイヤに代わって銅ワイヤが使用されるケースが増えており、コストダウンと信頼性向上に貢献しています。

モールド工程によるパッケージ封止

モールド工程は、ダイスとボンディングワイヤを樹脂で封止し、外部環境から保護する工程です。一般的には、エポキシ系の成形樹脂が使用されます。高温に加熱された樹脂を金型内に流し込み、加圧・冷却することでパッケージが形成されます。

モールド工程では、樹脂の流動性や硬化条件、金型の設計などが重要なポイントとなります。ボイドと呼ばれる気泡の発生を防ぎ、ワイヤの変形やダイスへの応力を最小限に抑えることが求められます。また、パッケージの寸法精度や外観品質も検査項目となります。

近年では、薄型パッケージや多ピンパッケージなど、多様なパッケージ形態に対応するためのモールド技術が開発されています。また、環境負荷低減の観点から、ハロゲンフリーの樹脂材料も広く使用されるようになっています。

出荷前の最終検査項目

後工程の最終段階では、完成したICパッケージの品質を確認するための検査が行われます。この検査では、電気的特性、信頼性、外観品質などが評価されます。

電気的特性検査では、ICチップの動作や性能を確認するためのテストが実施されます。パッケージをテスト用ソケットに装着し、各種の信号を入力して出力を測定します。高速・高精度のテスト装置を使用することで、大量のICを効率的に検査することができます。

信頼性試験では、温度サイクルや高温高湿、振動などの過酷な環境条件下でICパッケージの耐久性を評価します。また、長期的な信頼性を確認するためのバーンイン試験も行われます。これらの試験により、実使用環境での不具合を未然に防ぐことができます。

外観検査では、パッケージの寸法や形状、マーキングの品質などを目視や自動検査装置でチェックします。ピンの曲がりや樹脂のバリ、傷などの欠陥が無いことを確認し、出荷基準を満たした製品のみが合格となります。

これらの検査を通過したICパッケージは、出荷されて電子機器のさまざまな部品として活躍することになります。

半導体製造における重要ポイント

半導体製造は、高度な技術と厳格な品質管理が求められる複雑なプロセスです。ここでは、半導体製造における重要なポイントについて解説します。

クリーンルーム環境の重要性

半導体製造における最も重要な要素の一つが、クリーンルーム環境です。半導体の微細な回路パターンは、ごくわずかなパーティクルや汚れによっても損傷を受ける可能性があります。そのため、製造工程全体を通して、厳格に管理された超清浄な環境を維持することが不可欠なのです。

クリーンルームでは、空気中のパーティクルや化学物質、温度や湿度などが常に監視・制御されています。加えて、作業者は特殊な無塵服を着用し、人体から発生するパーティクルを最小限に抑える必要があります。こうした徹底した管理により、高品質な半導体の製造が可能となるのです。

歩留まり向上のための品質管理

半導体製造におけるもう一つの重要なポイントが、歩留まり(良品率)の管理です。半導体の製造コストは非常に高く、歩留まりの僅かな変動が企業の収益性に大きく影響します。そのため、各工程における厳密な品質管理と不良品の早期発見・除外が欠かせません。

具体的には、ウエハーの各製造工程において、パターンの寸法や形状、膜厚などを厳しく検査します。また、完成したウエハーやパッケージに対しても、電気的特性の検査を実施し、不良品を取り除きます。こうした一連の品質管理により、歩留まりを最大化し、コスト競争力を維持することが可能となります。

微細化技術の進歩と限界

半導体の高性能化・高集積化を支えているのが、微細化技術の進歩です。微細化とは、トランジスタなどの素子サイズを縮小することで、チップ上により多くの素子を集積する技術のことを指します。例えば、5nmプロセス技術では、トランジスタの寸法がわずか数ナノメートルにまで微細化されています。

しかし、微細化にはいくつかの技術的な限界もあります。例えば、光の回折限界により、現在の光リソグラフィ技術では20nm以下の微細化が困難とされています。また、微細化にともない、トランジスタ間の干渉やリーク電流の増大などの問題も顕在化しつつあります。こうした限界を打ち破るために、EUVリソグラフィをはじめとする新たな微細化技術の開発が進められているのです。

半導体製造に求められる高度な技術力

ここまで見てきたように、半導体の製造には非常に高度で専門的な技術力が必要とされます。例えば、フォトリソグラフィ工程では、ナノメートルオーダーの回路パターンを正確に露光・転写する技術が求められます。また、成膜工程では、原子レベルで膜厚を制御する技術が、イオン注入工程では、ウエハー内の不純物濃度を精密に制御する技術が必要不可欠です。

加えて、これらの個別の要素技術を、歩留まりを維持しながら大量生産するためには、生産技術や歩留まり管理のノウハウなども欠かせません。言い換えれば、半導体製造は、材料、デバイス、プロセス、装置、分析・管理など、多岐にわたる専門技術が高度に融合されることで成り立っているのです。

半導体製造の重要ポイントをまとめると、クリーンルーム環境の維持、歩留まりの管理、微細化技術の進歩、そして高度な専門技術の融合、ということができるでしょう。これらを支えているのが、長年にわたって蓄積されてきた半導体メーカー各社の技術力であり、今後もさらなる技術革新が期待される分野だと言えます。

まとめ

半導体製造の工程は、シリコンウエハーの製造、前工程、後工程の大きく3つに分けられます。

シリコンウエハーは、珪石から高純度シリコンを経て、単結晶化、スライシング、研磨の工程を経て製造されます。その後の前工程では、フォトリソグラフィ、成膜、エッチング、イオン注入、熱処理などの技術を駆使しシリコンウエハー上に複雑な回路パターンを形成し、後工程では、ダイシング、ボンディング、モールド、検査の工程を経て完成したICチップがパッケージ化されます。

これらの工程全体を通して、クリーンルーム環境の維持、歩留まりの管理、微細化技術の進歩が重要なポイントとなります。半導体製造には、材料、デバイス、プロセス、装置、分析・管理など、多岐にわたる高度な専門技術の融合が不可欠なのです。

- 関連記事:パーティクル問題解決の最前線!半導体品質向上のための対策術

- 関連記事:【FOUPがもたらす半導体革新】品質管理はどう変わる?

- 関連記事:【バッチ式vs枚葉式】半導体製造装置の2大方式を徹底比較

- 関連記事:半導体製造装置が丸わかり!装置選びのポイントと選定のコツ

- 関連記事:MES導入で生産性向上!活用法を3つご紹介

- 関連記事:MES(製造実行システム)とは?導入のメリットや事例、ERPとの違い

- 関連記事:MES活用例:「設備・人の稼働データ」と「工程実績データ」

参考文献:

https://www.semiconductor-industry.com/process/